November 07, 2003

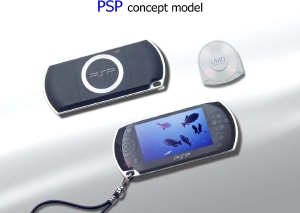

SONY PSP CONCEPT MODEL

SONY PSP「プレイステーションポータブル」

来年末のクリスマス商戦に参戦?とかApple iPod対抗商品とかいろいろ噂がありますが、SONYの未来を占う商品になりそうですな。

PSP CPU Core -

MIPS R4000 32-bit core

128-bit bus

1-333MHz (1.2V)

8MB eDRAM main memory

2.6Gbps bus bandwidth

FPU, VFPU (2.6 billion flops)

3D graphics extended instructions

I Cache, D Cache

PSP Media Engine -

MIPS R4000 32-bit core

128-bit bus

1-333MHz (1.2V)

2MB eDRAM submemory

I-Cache, D-Cache

90nm CMOS

PSP Graphics Core -

1-166MHz (1.2V)

256-bit bus

2MB eDRAM (VRAM)

5.3Gbps bus bandwidth

664 million pixels per second pizel fill rate

3D curved surface and 3D polygon engine

Support for compressed textures, hardware clipping, morphing, bone, tessellation, bezier, b-spline (NURBS)

Maximum of 33 million polygons per second

24-bit full color (RGBA)

Sound Core -

VME (Virtual Mobile Engine)

Reconfigurable DSP

166MHz (1.2 V)

128-bit bus

5 giga operations per second

CODEC capabilities

3D sound, 7.1 channels

Synthesizer, effecter, and other abilities

ATRAC3 plus, AAC, MP3 for audio

Media -

UMD (Universal Media Disc)

60mm-diameter disc

660nm laser diode

1.8GB capacity (dual-layered disc)

11Mbps transfer rate

AES crypto system

Unique disc ID

Shock proof

Regional code system

Parental lock system

Repeat ordering system

Other Specifications -

16:9-format widescreen TFT LCD (480x272 pixels, 24-bit full color)

MPEG4 AVC decoder

Wireless LAN (802.11)

IrDA (Infrared Data Association)

USB 2.0

Memory Stick

AV in/out

Stereo headphone out

Lithium ion battery

Expansion port

Trackback on "SONY PSP CONCEPT MODEL"

このエントリーのトラックバックURL:

"SONY PSP CONCEPT MODEL"へのトラックバックはまだありません。

http://www003.upp.so-net.ne.jp/ken_o/fink.html

Fink設定編

過去のFinkに関連するページを抽出しています.

参考になります。